# High Performance Datacenter Networks

Architectures, Algorithms, and Opportunities

# Synthesis Lectures on Computer Architecture

#### Editor

2010

### Mark D. Hill, University of Wisconsin

Synthesis Lectures on Computer Architecture publishes 50- to 100-page publications on topics pertaining to the science and art of designing, analyzing, selecting and interconnecting hardware components to create computers that meet functional, performance and cost goals. The scope will largely follow the purview of premier computer architecture conferences, such as ISCA, HPCA, MICRO, and ASPLOS.

High Performance Datacenter Networks: Architectures, Algorithms, and Opportunities Dennis Abts and John Kim 2011

## Quantum Computing for Architects, Second Edition Tzvetan Metodi, Fred Chong, and Arvin Faruque 2011

Processor Microarchitecture: An Implementation Perspective Antonio González, Fernando Latorre, and Grigorios Magklis 2010

### Transactional Memory, 2nd edition Tim Harris, James Larus, and Ravi Rajwar 2010

Computer Architecture Performance Evaluation Methods Lieven Eeckhout

# Introduction to Reconfigurable Supercomputing

Marco Lanzagorta, Stephen Bique, and Robert Rosenberg 2009

# On-Chip Networks Natalie Enright Jerger and Li-Shiuan Peh

# The Memory System: You Can't Avoid It, You Can't Ignore It, You Can't Fake It

Bruce Jacob

2009

# Fault Tolerant Computer Architecture

Daniel J. Sorin 2009

# The Datacenter as a Computer: An Introduction to the Design of Warehouse-Scale Machines free access

Luiz André Barroso and Urs Hölzle 2009

# Computer Architecture Techniques for Power-Efficiency

Stefanos Kaxiras and Margaret Martonosi 2008

# Chip Multiprocessor Architecture: Techniques to Improve Throughput and Latency

Kunle Olukotun, Lance Hammond, and James Laudon 2007

### Transactional Memory

James R. Larus and Ravi Rajwar 2006

# Quantum Computing for Computer Architects

Tzvetan S. Metodi and Frederic T. Chong 2006

# Copyright © 2011 by Morgan & Claypool

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means—electronic, mechanical, photocopy, recording, or any other except for brief quotations in printed reviews, without the prior permission of the publisher.

High Performance Datacenter Networks: Architectures, Algorithms, and Opportunities

Dennis Abts and John Kim

www.morganclaypool.com

ISBN: 9781608454020 paperback ISBN: 9781608454037 ebook

DOI 10.2200/S00341ED1V01Y201103CAC014

A Publication in the Morgan & Claypool Publishers series SYNTHESIS LECTURES ON COMPUTER ARCHITECTURE

Lecture #14

Series Editor: Mark D. Hill, University of Wisconsin

Series ISSN

Synthesis Lectures on Computer Architecture Print 1935-3235 Electronic 1935-3243

# High Performance Datacenter Networks

Architectures, Algorithms, and Opportunities

Dennis Abts

Google Inc.

John Kim

Korea Advanced Institute of Science and Technology (KAIST)

SYNTHESIS LECTURES ON COMPUTER ARCHITECTURE #14

# **ABSTRACT**

Datacenter networks provide the communication substrate for large parallel computer systems that form the ecosystem for high performance computing (HPC) systems and modern Internet applications. The design of new datacenter networks is motivated by an array of applications ranging from communication intensive climatology, complex material simulations and molecular dynamics to such Internet applications as Web search, language translation, collaborative Internet applications, streaming video and voice-over-IP. For both Supercomputing and Cloud Computing the network enables distributed applications to communicate and interoperate in an orchestrated and efficient way.

This book describes the design and engineering tradeoffs of datacenter networks. It describes interconnection networks from topology and network architecture to routing algorithms, and presents opportunities for taking advantage of the emerging technology trends that are influencing router microarchitecture. With the emergence of "many-core" processor chips, it is evident that we will also need "many-port" routing chips to provide a bandwidth-rich network to avoid the performance limiting effects of Amdahl's Law. We provide an overview of conventional topologies and their routing algorithms and show how technology, signaling rates and cost-effective optics are motivating new network topologies that scale up to millions of hosts. The book also provides detailed case studies of two high performance parallel computer systems and their networks.

# **KEYWORDS**

network architecture and design, topology, interconnection networks, fiber optics, parallel computer architecture, system design

# Contents

|   | Pref  | Preface xi  Acknowledgments xiii             |  |  |  |  |

|---|-------|----------------------------------------------|--|--|--|--|

|   | Ack   |                                              |  |  |  |  |

|   | Note  | e to the Reader                              |  |  |  |  |

| 1 | Intro | oduction                                     |  |  |  |  |

|   | 1.1   | From Supercomputing to Cloud Computing       |  |  |  |  |

|   | 1.2   | Beowulf: The Cluster is Born                 |  |  |  |  |

|   | 1.3   | Overview of Parallel Programming Models      |  |  |  |  |

|   | 1.4   | Putting it all together 5                    |  |  |  |  |

|   | 1.5   | Quality of Service (QoS) requirements        |  |  |  |  |

|   | 1.6   | Flow control                                 |  |  |  |  |

|   |       | 1.6.1 Lossy flow control                     |  |  |  |  |

|   |       | 1.6.2 Lossless flow control                  |  |  |  |  |

|   | 1.7   | The rise of ethernet                         |  |  |  |  |

|   | 1.8   | Summary                                      |  |  |  |  |

| 2 | Bacl  | kground                                      |  |  |  |  |

|   | 2.1   | Interconnection networks                     |  |  |  |  |

|   | 2.2   | Technology trends                            |  |  |  |  |

|   | 2.3   | Topology, Routing and Flow Control           |  |  |  |  |

|   | 2.4   | Communication Stack                          |  |  |  |  |

| 3 | Торо  | ology Basics                                 |  |  |  |  |

|   | 3.1   | Introduction                                 |  |  |  |  |

|   | 3.2   | Types of Networks                            |  |  |  |  |

|   | 3.3   | Mesh, Torus, and Hypercubes                  |  |  |  |  |

|   |       | 3.3.1 Node identifiers                       |  |  |  |  |

|   |       | 3.3.2 <i>k</i> -ary <i>n</i> -cube tradeoffs |  |  |  |  |

| 4 | High | h-Radix Topologies                                        |

|---|------|-----------------------------------------------------------|

|   | 4.1  | Towards High-radix Topologies                             |

|   | 4.2  | Technology Drivers                                        |

|   |      | 4.2.1 Pin Bandwidth                                       |

|   |      | 4.2.2 Economical Optical Signaling                        |

|   | 4.3  | High-Radix Topology                                       |

|   |      | 4.3.1 High-Dimension Hypercube, Mesh, Torus               |

|   |      | 4.3.2 Butterfly                                           |

|   |      | 4.3.3 High-Radix Folded-Clos                              |

|   |      | 4.3.4 Flattened Butterfly                                 |

|   |      | 4.3.5 Dragonfly                                           |

|   |      | 4.3.6 HyperX                                              |

| 5 | Rou  | ting                                                      |

|   | 5.1  | Routing Basics                                            |

|   | 3.1  | 5.1.1 Objectives of a Routing Algorithm                   |

|   | 5.2  | Minimal Routing                                           |

|   | 3.2  | 5.2.1 Deterministic Routing                               |

|   |      | 5.2.2 Oblivious Routing                                   |

|   | 5.3  | Non-minimal Routing                                       |

|   |      | 5.3.1 Valiant's algorithm (VAL)                           |

|   |      | 5.3.2 Universal Global Adaptive Load-Balancing (UGAL)     |

|   |      | 5.3.3 Progressive Adaptive Routing (PAR)                  |

|   |      | 5.3.4 Dimensionally-Adaptive, Load-balanced (DAL) Routing |

|   | 5.4  | Indirect Adaptive Routing                                 |

|   | 5.5  | Routing Algorithm Examples                                |

|   |      | 5.5.1 Example 1: Folded-Clos                              |

|   |      | 5.5.2 Example 2: Flattened Butterfly                      |

|   |      | 5.5.3 Example 3: Dragonfly                                |

| 6 | Scal | able Switch Microarchitecture                             |

|   | 6.1  | Router Microarchitecture Basics                           |

|   | 6.2  | Scaling baseline microarchitecture to high radix          |

|   | 6.3  | Fully Buffered Crossbar                                   |

|   | 6.4  | Hierarchical Crossbar Architecture                        |

|   | 6.5  | Examples of High-Radix Routers                            |

|   |       | 6.5.1 Cray YARC Router                 |

|---|-------|----------------------------------------|

|   |       | 6.5.2 Mellanox InfiniScale IV          |

| 7 | Syste | em Packaging                           |

|   | 7.1   | Packaging hierarchy                    |

|   | 7.2   | Power delivery and cooling             |

|   | 7.3   | Topology and Packaging Locality        |

| 8 | Case  | Studies                                |

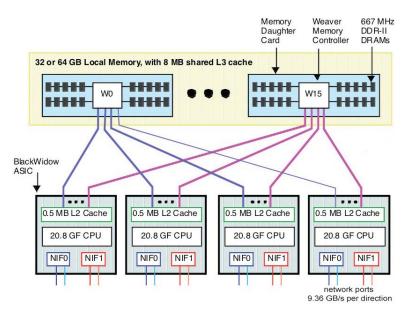

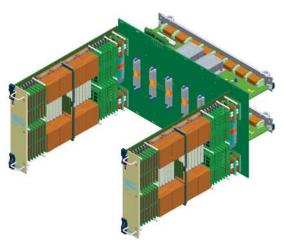

|   | 8.1   | Cray BlackWidow Multiprocessor         |

|   |       | 8.1.1 BlackWidow Node Organization     |

|   |       | 8.1.2 High-radix Folded-Clos Network   |

|   |       | 8.1.3 System Packaging                 |

|   |       | 8.1.4 High-radix Fat-tree              |

|   |       | 8.1.5 Packet Format                    |

|   |       | 8.1.6 Network Layer Flow Control       |

|   |       | 8.1.7 Data-link Layer Protocol         |

|   |       | 8.1.8 Serializer/Deserializer          |

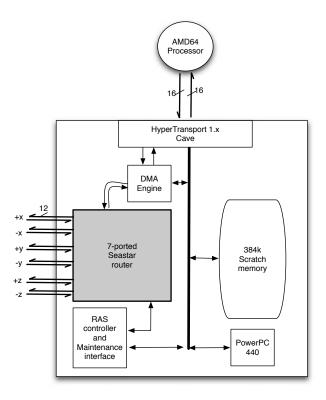

|   | 8.2   | Cray XT Multiprocessor                 |

|   |       | 8.2.1 3-D torus                        |

|   |       | 8.2.2 Routing                          |

|   |       | 8.2.3 Flow Control                     |

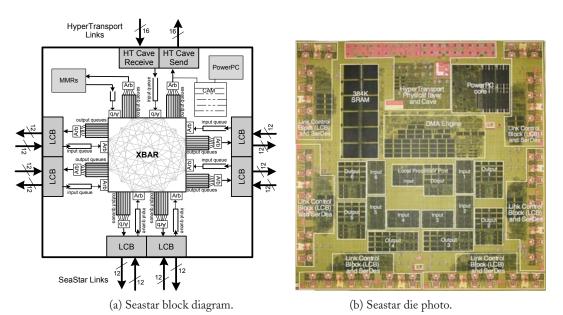

|   |       | 8.2.4 SeaStar Router Microarchitecture |

|   | 8.3   | Summary                                |

| 9 | Clos  | sing Remarks                           |

|   | 9.1   | Programming models                     |

|   | 9.2   | Wire protocols                         |

|   | 9.3   | Opportunities                          |

|   | Bibli | iography                               |

|   | Auth  | nors' Biographies                      |

# **Preface**

This book is aimed at the researcher, graduate student and practitioner alike. We provide some background and motivation to provide the reader with a substrate upon which we can build the new concepts that are driving high-performance networking in both supercomputing and cloud computing. We assume the reader is familiar with computer architecture and basic networking concepts. We show the evolution of high-performance interconnection networks over the span of two decades, and the underlying technology trends driving these changes. We describe how to apply these technology drivers to enable new network topologies and routing algorithms that scale to millions of processing cores. We hope that practitioners will find the material useful for making design tradeoffs, and researchers will find the material both timely and relevant to modern parallel computer systems which make up today's datacenters.

Dennis Abts and John Kim March 2011

# Acknowledgments

While we draw from our experience at Cray and Google and academic work on the design and operation of interconnection networks, most of what we learned is the result of hard work, and years of experience that have led to practical insights. Our experience benefited tremendously from our colleagues Steve Scott at Cray, and Bill Dally at Stanford University. In addition, many hours of whiteboard-huddled conversations with Mike Marty, Philip Wells, Hong Liu, and Peter Klausler at Google. We would also like to thank Google colleagues James Laudon, Bob Felderman, Luiz Barroso, and Urs Hölzle for reviewing draft versions of the manuscript. We want to thank the reviewers, especially Amin Vahdat and Mark Hill for taking the time to carefully read and provide feedback on early versions of this manuscript. Thanks to Urs Hölzle for guidance, and Kristin Weissman at Google and Michael Morgan at Morgan & Claypool Publishers. Finally, we are grateful for Mark Hill and Michael Morgan for inviting us to this project and being patient with deadlines.

Finally, and most importantly, we would like to thank our loving family members who graciously supported this work and patiently allowed us to spend our free time to work on this project. Without their enduring patience and with an equal amount of prodding, this work would not have materialized.

Dennis Abts and John Kim March 2011

# Note to the Reader

We very much appreciate any feedback, suggestions, and corrections you might have on our manuscript. The Morgan & Claypool publishing process allows a lightweight method to revise the electronic edition. We plan to revise the manuscript relatively often, and will gratefully acknowledge any input that will help us to improve the accuracy, readability, or general usefulness of the book. Please leave your feedback at http://tinyurl.com/HPNFeedback

Dennis Abts and John Kim March 2011

# Introduction

Today's datacenters have emerged from the collection of loosely connected workstations, which shaped the humble beginnings of the Internet, and grown into massive "warehouse-scale computers" (Figure 1.1) capable of running the most demanding workloads. Barroso and Hölzle describe the architecture of a warehouse-scale computer (WSC) [9] and give an overview of the programming model and common workloads executed on these machines. The hardware building blocks are packaged into "racks" of about 40 servers, and many racks are interconnected using a high-performance network to form a "cluster" with hundreds or thousands of *tightly-coupled* servers for performance,

Figure 1.1: A datacenter with cooling infrastructure and power delivery highlighted.

#### 2 1. INTRODUCTION

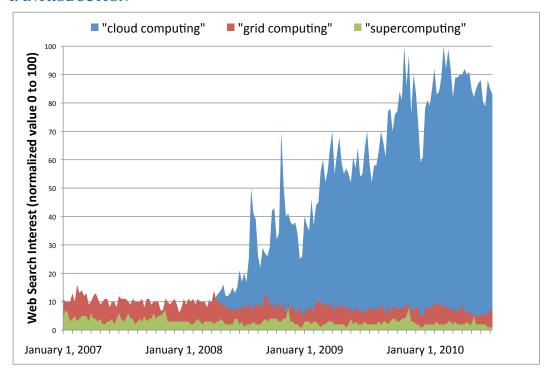

Figure 1.2: Comparison of web search interest and terminology.

but *loosely-coupled* for fault tolerance and isolation. This highlights some distinctions between what have traditionally been called "supercomputers" and what we now consider "cloud computing," which appears to have emerged around 2008 (based on the relative Web Search interest shown in Figure 1.2) as a moniker for *server-side* computing. Increasingly, our computing needs are moving away from desktop computers toward more mobile clients (e.g., smart phones, tablet computers, and netbooks) that depend on Internet services, applications, and storage. As an example, it is much more efficient to maintain a repository of digital photography on a server in the "cloud" than on a PC-like computer that is perhaps not as well maintained as a server in a large datacenter, which is more reminiscent of a clean room environment than a living room where your precious digital memories are subjected to the daily routine of kids, spills, power failures, and varying temperatures; in addition, most consumers upgrade computers every few years, requiring them to migrate *all* their precious data to their newest piece of technology. In contrast, the "cloud" provides a clean, temperature controlled environment with ample power distribution and backup. Not to mention your data in the "cloud" is probably replicated for redundancy in the event of a hardware failure the user data is replicated and restored generally without the user even aware that an error occurred.

# 1.1 FROM SUPERCOMPUTING TO CLOUD COMPUTING

As the ARPANET transformed into the Internet over the past forty years, and the World Wide Web emerges from adolescence and turns twenty, this metamorphosis has seen changes in both supercomputing and cloud computing. The supercomputing industry was born in 1976 when Seymour Cray announced the Cray-1 [54]. Among the many innovations were its processor design, process technology, system packaging, and instruction set architecture. The foundation of the architecture was based on the notion of vector operations that allowed a single instruction to operate on an array, or "vector," of elements simultaneously. In contrast to scalar processors of the time whose instructions operated on single data items. The vector parallelism approach dominated the high-performance computing landscape for much of the 1980s and early 1990s until "commodity" microprocessors began aggressively implementing forms of instruction-level parallelism (ILP) and better cache memory systems to exploit spatial and temporal locality exhibited by most applications. Improvements in CMOS process technology and full-custom CMOS design practices allowed microprocessors to quickly ramp up clock rates to several gigahertz. This coupled with multi-issue pipelines; efficient branch prediction and speculation eventually allowed microprocessors to catch up with their proprietary vector processors from Cray, Convex, and NEC. Over time, conventional microprocessors incorporated short vector units (e.g., SSE, MMX, AltiVec) into the instruction set. However, the largest beneficiary of vector processing has been multimedia applications as evidenced by the jointly developed (by Sony, Toshiba, and IBM) Cell processor which found widespread success in Sony's Playstation3 game console, and even some special-purpose computer systems like Mercury Systems.

Parallel applications eventually have to synchronize and communicate among parallel threads. Amdahl's Law is relentless and unless enough parallelism is exposed, the time spent orchestrating the parallelism and executing the sequential region will ultimately limit the application performance [27].

# 1.2 BEOWULF: THE CLUSTER IS BORN

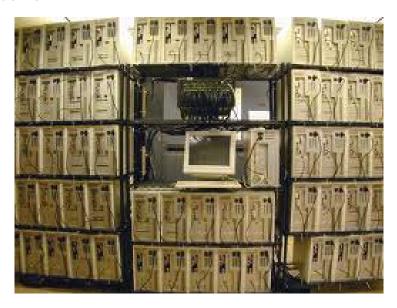

In 1994 Thomas Sterling (then dually affiliated with the California Institute of Technology and NASAs JPL) and Donald Becker (then a researcher at NASA) assembled a parallel computer that became known as a *Beowulf* cluster<sup>1</sup>. What was unique about Beowulf [61] systems was that they were built from common "off-the-shelf" computers, as Figure 1.3 shows, system packaging was not an emphasis. More importantly, as a loosely-coupled distributed memory machine, Beowulf forced researchers to think about *how* to efficiently program parallel computers. As a result, we benefited from portable and free programming interfaces such as parallel virtual machines (PVM), message passing interfaces (MPICH and OpenMPI), local area multiprocessor (LAM); with MPI being embraced by the HPC community and highly optimized.

The Beowulf cluster was organized so that one machine was designated the "server," and it managed job scheduling, pushing binaries to clients, and monitoring. It also acted as the gateway

<sup>&</sup>lt;sup>1</sup>The genesis of the name comes from the poem which describes Beowulf as having "thirty men's heft of grasp in the gripe of his hand."

#### 4 1. INTRODUCTION

Figure 1.3: An 128 processor Beowulf cluster at NASA.

to the "outside world," so researchers had a login host. The model is still quite common: with some nodes being designated as service and IO nodes where users actually login to the parallel machine. From there, they can compile their code, and launch the job on "compute only" nodes — the worker bees of the colony — and console information, machine status is communicated to the service nodes.

# 1.3 OVERVIEW OF PARALLEL PROGRAMMING MODELS

Early supercomputers were able to work efficiently, in part, because they shared a common *physical* memory space. As a result, communication among processors was very efficient as they updated shared variables and operated on common data. However, as the size of the systems grew, this shared memory model evolved into a *distributed shared memory* (DSM) model where each processing node owns a portion of the machines physical memory and the programmer is provided with a *logically shared* address space making it easy to reason about how the application is partitioned and communication among threads. The Stanford DASH [45] was the first to demonstrate this cachecoherent non-uniform memory (ccNUMA) access model, and the SGI Origin2000 [43] was the first machine to successfully commercialize the DSM architecture.

We commonly refer to *distributed memory* machines as "clusters" since they are loosely-coupled and rely on message passing for communication among processing nodes. With the inception of Beowulf clusters, the HPC community realized they could build modest-sized parallel computers on

a relatively small budget. To their benefit, the common benchmark for measuring the performance of a parallel computer is LINPACK, which is not communication intensive, so it was commonplace to use inexpensive Ethernet networks to string together commodity nodes. As a result, Ethernet got a foothold on the list of the TOP500 [62] civilian supercomputers with almost 50% of the TOP500 systems using Ethernet.

# 1.4 PUTTING IT ALL TOGETHER

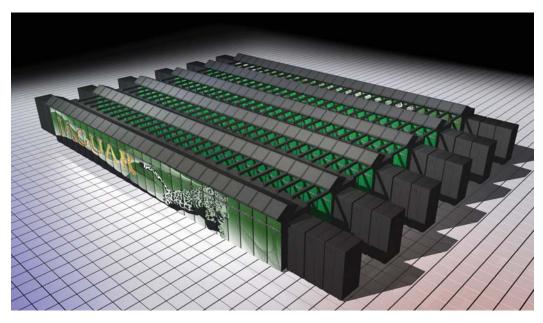

The first Cray-1 [54] supercomputer had expected to ship one system per quarter in 1977. Today, microprocessor companies have refined their CMOS processes and manufacturing making them very cost-effective building blocks for large-scale parallel systems capable of 10s of petaflops. This shift away from "proprietary" processors and trend toward "commodity" processors has fueled the growth of systems. At the time of this writing, the largest computer on the TOP500 list [62] has in excess of 220,000 cores (see Figure 7.5) and consumes almost seven megawatts!

A datacenter server has many commonalities as one used in a supercomputer, however, there are also some very glaring differences. We enumerate several properties of both a warehouse-scale computer (WSC) and a supercomputer (Cray XE6).

#### Datacenter server

- Sockets per server 2 sockets x86 platform

- Memory capacity 16 GB DRAM

- **Disk capacity** 5×1TB disk drive, and 1×160GB SSD (FLASH)

- Compute density 80 sockets per rack

- Network bandwidth per rack 1×48-port GigE switch with 40 down links, and 8 uplinks (5× oversubscription)

- Network bandwidth per socket 100 Mb/s if 1 GigE rack switch, or 1 Gb/s if 10 GigE rack switch

#### Supercomputer server

- Sockets per server 8 sockets x86 platform

- Memory capacity 32 or 64 GB DRAM

- Disk capacity IO capacity varies. Each XIO blade has four PCIe-Gen2 interfaces, for a total of 96 PCIe-Gen2 ×16 IO devices for a peak IO bandwidth of 768 GB/s per direction.

- Compute density 192 sockets per rack

#### 6 1. INTRODUCTION

- Network bandwidth per rack 48×48-port Gemini switch chips each with 160 GB/s switching bandwidth

- Network bandwidth per socket 9.6GB/s injection bandwidth with non-coherent Hyper-Transport 3.0 (ncHT3)

Several things stand out as differences between a datacenter server and supercomputer node. First, the *compute density* for the supercomputer is significantly better than a standard 40U rack. On the other hand, this dense packaging also puts pressure on cooling requirements not to mention power delivery. As power and its associated delivery become increasingly expensive, it becomes more important to optimize the number of operations per watt; often the *size* of a system is limited by power distribution and cooling infrastructure.

Another point is the vast difference in *network bandwidth per socket* in large part because ncHT3 is a much higher bandwidth processor interface than PCIe-Gen2, however, as PCI-Gen3×16 becomes available we expect that gap to narrow.

# 1.5 QUALITY OF SERVICE (QOS) REQUIREMENTS

With HPC systems it is commonplace to dedicate the system for the duration of application execution. Allowing *all* processors to be used for compute resources. As a result, there is no need for *performance isolation* from competing applications. *Quality of Service (QoS)* provides both performance isolation *and differentiated service* for applications<sup>2</sup>. Cloud computing often has a varied workloads requiring multiple applications to share resources. *Workload consolidation* [33] is becoming increasingly important as memory and processor cost increase, as a result so does the value of increased system utilization.

The QoS *class* refers to the end-to-end class of service as observed by the application. In principle, QoS is divided into three categories:

**Best effort** - traffic is treated as a FIFO with no differentiation provided.

**Differentiated service** - also referred to as "soft QoS" where traffic is given a statistical preference over other traffic. This means it is less likely to be dropped relative to best effort traffic, for example, resulting in lower average latency and increased average bandwidth.

**Guaranteed service** - also referred to as "hard QoS" where a fraction of the network bandwidth is reserved to provide no-loss, low jitter bandwidth guarantees.

In practice, there are many intermediate pieces which are, in part, responsible for implementing a QoS scheme. A routing algorithm determines the set of usable paths through the network between any source and destination. Generally speaking, routing is a background process that attempts to load-balance the physical links in the system taking into account any network faults and programming

<sup>&</sup>lt;sup>2</sup>We use the term "applications" loosely here to represent processes or threads, at whatever granularity a service level agreement is applied.

the forwarding tables within each router. When a new packet arrives, the header is inspected and the network address of the destination is used to index into the forwarding table which emits the output port where the packet is scheduled for transmission. The "packet forwarding" process is done on a packet-by-packet basis and is responsible for identifying packets marked for special treatment according to its QoS class.

The basic unit over which a QoS class is applied is the flow. A flow is described as a tuple (SourceIP, SourcePort, DestIP, DestPort). Packets are marked by the host or edge switch using either 1) port range, or 2) host (sender/client-side) marking. Since we are talking about end-to-end service levels, ideally the host which initiates the communication would request a specific level of service. This requires some client-side API for establishing the QoS requirements prior to sending a message. Alternatively, edge routers can mark packets as they are injected into the core fabric.

Packets are marked with their service class which is interpreted at each hop and acted upon by routers along the path. For common Internet protocols, the differentiated service (DS) field of the IP header provides this function as defined by the DiffServ [RFC2475] architecture for network layer QoS. For compatibility reasons, this is the same field as the type of service (ToS) field [RFC791] of the IP header. Since the RFC does not clearly describe how "low," "medium," or "high" are supposed to be interpreted, it is common to use five classes: best effort (BE), AF1, AF2, AF3, AF4, and set the drop priority to 0 (ignored).

#### 1.6 FLOW CONTROL

Surprisingly, a key difference in system interconnects is flow control. How the switch and buffer resources are managed is very different in Ethernet than what is typical in a supercomputer interconnect. There are several kinds of flow control in a large distributed parallel computer. The interconnection network is a shared resource among all the compute nodes, and network resources must be carefully managed to avoid corrupting data, overflowing a buffer, etc. The basic mechanism by which resources in the network are managed is flow control. Flow control provides a simple accounting method for managing resources that are in demand by multiple uncoordinated sources. The resource is managed in units of *flits* (flow control units). When a resource is requested but not currently available for use, we must decide what to do with the incoming request. In general, we can 1) drop the request and all subsequent requests until the resource is freed, or 2) block and wait for the request to free.

#### LOSSY FLOW CONTROL 1.6.1

With a lossy flow control [20, 48], the hardware can discard packets until there is room in the desired resource. This approach is usually applied to input buffers on each switch chip, but also applies to resources in the network interface controller (NIC) chip as well. When packets are dropped, the software layers must detect the loss, usually through an unexpected sequence number indicating that one or more packets are missing or out of order. The receiver software layers will discard packets that do not match the expected sequence number, and the sender software layers will detect that it

#### 8 1. INTRODUCTION

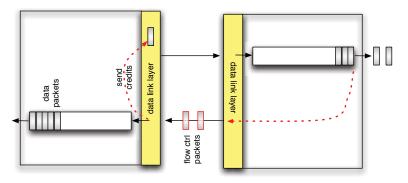

Figure 1.4: Example of credit-based flow control across a network link.

has not received an *acknowledgment* packet and will cause a sender timeout which prompts the "send window" — packets sent since the last acknowledgment was received — to be retransmitted. This algorithm is referred to as go-back-N since the sender will "go back" and retransmit the last N (send window) packets.

### 1.6.2 LOSSLESS FLOW CONTROL

Lossless flow control implies that packets are never dropped as a results of lack of buffer space (i.e., in the presence of congestion). Instead, it provides *back pressure* to indicate the absence of available buffer space in the resource being managed.

# 1.6.2.1 Stop/Go (XON/XOFF) flow control

A common approach is XON/XOFF or stop/go flow control. In this approach, the receiver provides simple handshaking to the sender indicating whether it is safe (XON) to transmit, or not (XOFF). The sender is able to send flits until the receiver asserts stop (XOFF). Then, as the receiver continues to process packets from the input buffer freeing space, and when a threshold is reached the receiver will assert the XON again allowing the sender to again start sending. This Stop/Go functionality correctly manages the resource and avoids overflow as long as the time at which XON is asserted again (i.e., the threshold level in the input buffer) minus the time XOFF is asserted and the buffer is sufficient to allow any in-flight flits to land. This slack in the buffer is necessary to act as a flow control shock absorber for outstanding flits necessary to cover the propagation delay of the flow control signals.

#### 1.6.2.2 Credit-based flow control

Credit based flow control (Figure 1.4) provides more efficient use of the buffer resources. The sender maintains a count of the number of available *credits*, which represent the amount of free space in the receiver's input buffer. A separate count is used for each virtual channel (VC) [21]. When a new

packet arrives at the output port, the sender checks the available credit counter. For wormhole flow control [20] across the link, the sender's available credit needs to only be one or more. For virtual cut-through (VCT) [20, 22] flow control across the link, the sender's available credit must be more than the size of the packet. In practice, the switch hardware doesn't have to track the size of the packet in order to allow VCT flow control. The sender can simply check the available credit count is larger than the maximum packet size.

# 1.7 THE RISE OF ETHERNET

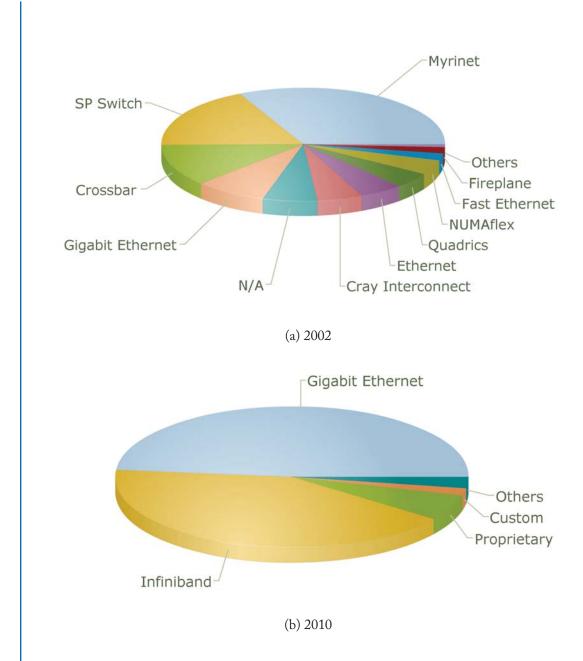

It may be an extreme example comparing a typical datacenter server to a state-of-the-art supercomputer node, but the fact remains that Ethernet is gaining a significant foothold in the high-performance computing space with nearly 50% of the systems on the TOP500 list [62] using Gigabit Ethernet as shown in Figure 1.5(b). Infiniband (includes SDR, DDR and QDR) accounts for 41% of the interconnects leaving very little room for proprietary networks. The landscape was very different in 2002, as shown in Figure 1.5(a), where Myrinet accounted for about one third of the system interconnects. The IBM SP2 interconnect accounted for about 18%, and the remaining 50% of the system interconnects were split among about nine different manufacturers. In 2002, only about 8% of the TOP500 systems used gigabit Ethernet, compared to the nearly 50% in June of 2010.

### 1.8 SUMMARY

No doubt "cloud computing" benefited from this wild growth and acceptance in the HPC community, driving prices down and making more reliable parts. Moving forward we may see even further consolidation as 40 Gig Ethernet converges with some of the Infiniband semantics with RDMA over Ethernet (ROE). However, a warehouse-scale computer (WSC) [9] and a supercomputer have different usage models. For example, most supercomputer applications expect to run on the machine in a dedicated mode, not having to compete for compute, network, or IO resources with *any* other applications.

Supercomputing applications will commonly checkpoint their dataset, since the MTBF of a large system is usually measured in 10s of hours. Supercomputing applications also typically run with a dedicated system, so QoS demands are not typically a concern. On the other hand, a datacenter will run a wide variety of applications, some user-facing like Internet email, and others behind the scenes. The workloads vary drastically, and programmers must learn that hardware can, and does, fail and the application must be fault-aware and deal with it gracefully. Furthermore, clusters in the datacenter are often shared across dozens of applications, so performance isolation and fault isolation are key to scaling applications to large processor counts.

Choosing the "right" topology is important to the overall system performance. We must take into account the flow control, QoS requirements, fault tolerance and resilience, as well as workloads to better understand the latency and bandwidth characteristics of the entire system. For example,

Figure 1.5: Breakdown of supercomputer interconnects from the Top500 list.

# 1.8. SUMMARY 11

topologies with abundant *path diversity* are able to find alternate routes between arbitrary endpoints. This is only one aspect of topology choice that we will consider in subsequent chapters.

# Background

Over the past three decades, Moore's Law has ushered in an era where transistors within a single silicon package are abundant; a trend that system architects took advantage of to create a class of many-core chip multiprocessors (CMPs) which interconnect many small processing cores using an on-chip network. However, the *pin density*, or number of signal pins per unit of silicon area, has not kept up with this pace. As a result *pin bandwidth*, the amount of data we can get on and off the chip package, has become a first-order design constraint and precious resource for system designers.

### 2.1 INTERCONNECTION NETWORKS

The components of a computer system often have to communicate to exchange status information, or data that is used for computation. The *interconnection network* is the substrate over which this communication takes place. Many-core CMPs employ an *on-chip* network for low-latency, high-bandwidth load/store operations between processing cores and memory, and among processing cores within a chip package.

Processor, memory, and its associated IO devices are often packaged together and referred to as a *processing node*. The *system-level* interconnection network connects all the processing nodes according to the network *topology*. In the past, system components shared a *bus* over which address and data were exchanged, however, this communication model did not scale as the number of components sharing the bus increased. Modern interconnection networks take advantage of high-speed signaling [28] with *point-to-point* serial links providing high-bandwidth connections between processors and memory in multiprocessors [29, 32], connecting input/output (IO) devices [31, 51], and as switching fabrics for routers.

# 2.2 TECHNOLOGYTRENDS

There are many considerations that go into building a large-scale cluster computer, many of which revolve around its cost effectiveness, in both *capital* (procurement) cost and *operating* expense. Although many of the components that go into a cluster each have different *technology* drivers which blurs the line that defines the optimal solution for both performance and cost. This chapter takes a look at a few of the technology drivers and how they pertain to the interconnection network.

The interconnection network is the substrate over which processors, memory and I/O devices interoperate. The underlying technology from which the network is built determines the data rate, resiliency, and cost of the network. Ideally, the processor, network, and I/O devices are all orchestrated

#### 14 2. BACKGROUND

in a way that leads to a cost-effective, high-performance computer system. The system, however, is no better than the components from which it is built.

The basic building block of the network is the *switch* (router) chip that interconnects the processing nodes according to some prescribed *topology*. The topology and how the system is packaged are closely related; typical packaging schemes are hierarchical – chips are packaged onto printed circuit boards, which in turn are packaged into an enclosure (e.g., rack), which are connected together to create a single system.

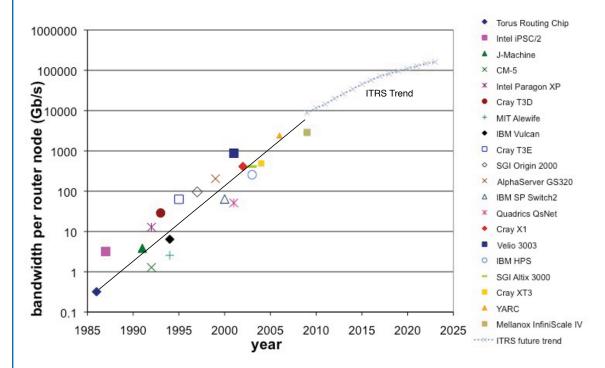

Figure 2.1: Off-chip bandwidth of prior routers, and ITRS predicted growth.

The past 20 years has seen several orders of magnitude increase in off-chip bandwidth spanning from several gigabits per second up to several terabits per second today. The bandwidth shown in Figure 2.1 plots the total pin bandwidth of a router – i.e., equivalent to the total number of signals times the signaling rate of each signal – and illustrates an exponential increase in pin bandwidth. Moreover, we expect this trend to continue into the next decade as shown by the International Roadmap for Semiconductors (ITRS) in Figure 2.1, with 1000s of pins per package and more than 100 Tb/s of off-chip bandwidth. Despite this exponential growth, pin and wire density simply does not match the growth rates of transistors as predicted by Moore's Law.

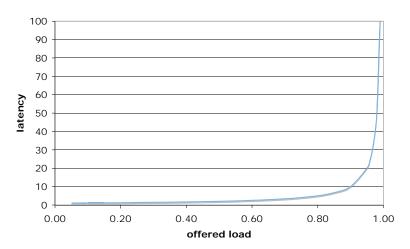

(a) Load versus latency for an ideal M/D/1 queue model.

**(b)** Measured data showing offered load (Mb/s) versus latency ( $\mu$ s) with average accepted throughput (Mb/s) overlaid to demonstrate saturation in a real network.

Figure 2.2: Network latency and bandwidth characteristics.

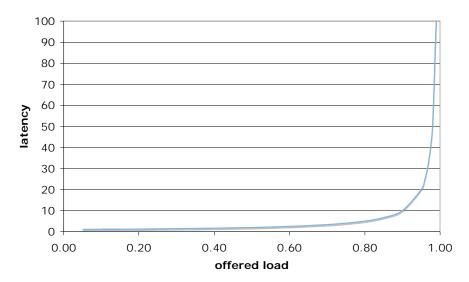

# 2.3 TOPOLOGY, ROUTING AND FLOW CONTROL

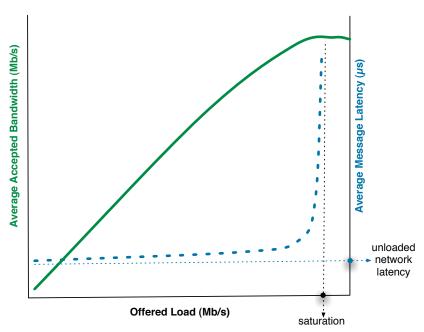

Before diving into details of what drives network performance, we pause to lay the ground work for some fundamental terminology and concepts. Network performance is characterized by its latency and bandwidth characteristics as illustrated in Figure 2.2. The queueing delay,  $Q(\lambda)$ , is a function of the offered load ( $\lambda$ ) and described by the latency-bandwidth characteristics of the network. An approximation of  $Q(\lambda)$  is given by an M/D/1 queue model, Figure 2.2(a). If we overlay the average accepted bandwidth observed by each node, assuming benign traffic, we Figure 2.2(b).

$$Q(\lambda) = \frac{1}{1 - \lambda} \tag{2.1}$$

When there is very low offered load on the network, the  $Q(\lambda)$  delay is negligible. However, as traffic intensity increases, and the network approaches saturation, the queueing delay will dominate the total packet latency.

The performance and cost of the interconnect are driven by a number of design factors, including topology, routing, flow control, and message efficiency. The *topology* describes how network nodes are interconnected and determines the *path diversity* — the number of distinct paths between any two nodes. The *routing algorithm* determines which path a packet will take in such as way as to *load balance* the physical links in the network. Network resources (primarily buffers for packet storage) are managed using a *flow control* mechanism. In general, flow control happens at the link-layer and possibly end-to-end. Finally, packets carry a *data payload* and the *packet efficiency* determines the *delivered* bandwidth to the application.

While recent *many-core* processors have spurred a  $2\times$  and  $4\times$  increase in the number of processing cores in each cluster, unless network performance keeps pace, the effects of Amdahl's Law will become a limitation. The topology, routing, flow control, and message efficiency all have first-order affects on the system performance, thus we will dive into each of these areas in more detail in subsequent chapters.

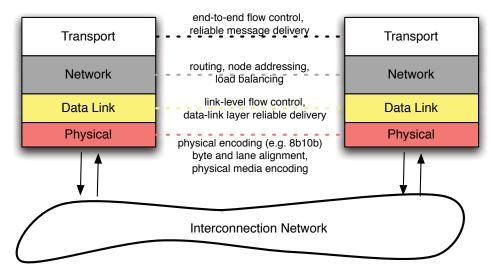

### 2.4 COMMUNICATION STACK

Layers of abstraction are commonly used in networking to provide fault isolation and device independence. Figure 2.3 shows the communication stack that is largely representative of the lower four layers of the OSI networking model. To reduce software overhead and the resulting end-toend latency, we want a thin networking stack. Some of the protocol processing that is common in Internet communication protocols is handled in specialized hardware in the network interface controller (NIC). For example, the *transport* layer provides reliable message delivery to applications and whether the protocol bookkeeping is done in software (e.g., TCP) or hardware (e.g., Infiniband reliable connection) directly affects the application performance. The *network* layer provides a logical namespace for endpoints (and possibly switches) in the system. The network layer handles *packets*, and provides the *routing* information identifying paths through the network among all source, destination pairs. It is the network layer that asserts routes, either at the source (i.e., source-routed)

**Figure 2.3:** The communication stack.

or along each individual hop (i.e., distributed routing) along the path. The data link layer provides link-level flow control to manage the receiver's input buffer in units of flits (flow control units). The lowest level of the protocol stack, the physical media layer, is where data is encoded and driven onto the medium. The physical encoding must maintain a DC-neutral transmission line and commonly uses 8b10b or 64b66b encoding to balance the transition density. For example, a 10-bit encoded value is used to represent 8-bits of data resulting in a 20% physical encoding overhead.

### **SUMMARY**

Interconnection networks are a critical component of modern computer systems. The emergence of cloud computing, which provides a homogenous cluster using conventional microprocessors and common Internet communication protocols aimed at providing Internet services (e.g., email, Web search, collaborative Internet applications, streaming video, and so forth) at large scale. While Internet services themselves may be insensitive to latency, since they operate on human timescales measured in 100s of milliseconds, the backend applications providing those services may indeed require large amounts of bandwidth (e.g., indexing the Web) and low latency characteristics. The programming model for cloud services is built largely around distributed message passing, commonly implemented around TCP (transport control protocol) as a conduit for making a remote procedure call (RPC).

Supercomputing applications, on the other hand, are often communication intensive and can be sensitive to network latency. The programming model may use a combination of shared memory and message passing (e.g., MPI) with often very fine-grained communication and synchronization

#### 18 2. BACKGROUND

needs. For example, *collective* operations, such as global sum, are commonplace in supercomputing applications and rare in Internet services. This is largely because Internet applications evolved from simple hardware primitives (e.g., low-cost ethernet NIC) and common communication models (e.g., TCP sockets) that were incapable of such operations.

As processor and memory performance continues to increase, the interconnection network is becoming increasingly important and largely determines the bandwidth and latency of remote memory access. Going forward, the emergence of *super datacenters* will convolve into *exa*-scale parallel computers.

# **Topology Basics**

The network *topology* — describing precisely how nodes are connected — plays a central role in both the performance and cost of the network. In addition, the topology drives aspects of the switch design (e.g., virtual channel requirements, routing function, etc), fault tolerance, and sensitivity to adversarial traffic. There are subtle yet very practical design issues that only arise *at scale*; we try to highlight those key points as they appear.

# 3.1 INTRODUCTION

Many scientific problems can be decomposed into a 3-D structure that represents the basic building blocks of the underlying phenomenon being studied. Such problems often have nearest neighbor communication patterns, for example, and lend themselves nicely to *k*-ary *n*-cube networks. A high-performance application will often use the system *dedicated* to provide the necessary performance isolation, however, a large production datacenter cluster will often run multiple applications simultaneously with varying workloads and often unstructured communication patterns.

The choice of topology is largely driven by two factors: technology and packaging constraints. Here, *technology* refers to the underlying silicon from which the routers are fabricated (i.e., node size, pin density, power, etc) and the signaling technology (e.g., optical versus electrical). The packaging constraints will determine the *compute density*, or amount of computation per unit of area on the datacenter floor. The packaging constraints will also dictate the data rate (signaling speed) and distance over which we can reliably communicate.

As a result of evolving technology, the topologies used in large-scale systems have also changed. Many of the earliest interconnection networks were designed using topologies such as butterflies or hypercubes, based on the simple observation that these topologies minimized hop count. Analysis by both Dally [18] and Agarwal [5] showed that under fixed packaging constraints, a *low-radix* network offered lower packet latency and thus better performance. Since the mid-1990s, *k*-ary *n*-cube networks were used by several high-performance multiprocessors such as the SGI Origin 2000 hypercube [43], the 2-D torus of the Cray X1 [16], the 3-D torus of the Cray T3E [55] and XT3 [12, 17] and the torus of the Alpha 21364 [49] and IBM BlueGene [35]. However, the increasing pin bandwidth has recently motivated the migration towards *high*-radix topologies such as the radix-64 folded-Clos topology used in the Cray BlackWidow system [56]. In this chapter, we will discuss mesh/torus topologies while in the next chapter, we will present high-radix topologies.

#### 20 3. TOPOLOGY BASICS

# 3.2 TYPES OF NETWORKS

Topologies can be broken down into two different genres: direct and indirect [20]. A direct network has processing nodes attached directly to the switching fabric; that is, the switching fabric is distributed among the processing nodes. An indirect network has the endpoint network independent of the endpoints themselves – i.e., dedicated switch nodes exist and packets are forwarded indirectly through these switch nodes. The type of network determines some of the packaging and cabling requirements as well as fault resilience. It also impacts cost, for example, since a direct network can combine the switching fabric and the network interface controller (NIC) functionality in the same silicon package. An indirect network typically has two separate chips, with one for the NIC and another for the switching fabric of the network. Examples of direct network include mesh, torus, and hypercubes discussed in this chapter as well as high-radix topologies such as the flattened butterfly described in the next chapter. Indirect networks include conventional butterfly topology and fat-tree topologies.

The term *radix* and *dimension* are often used to describe both types of networks but have been used differently for each network. For an indirect network, *radix* often refers to the number of ports of a switch, and the *dimension* is related to the number of stages in the network. However, for a direct network, the two terminologies are reversed – *radix* refers to the number of nodes within a dimension, and the network size can be further increased by adding multiple *dimensions*. The two terms are actually a duality of each other for the different networks – for example, in order to reduce the network diameter, the *radix* of an indirect network or the *dimension* of a direct network can be increased. To be consistent with existing literature, we will use the term *radix* to refer to different aspects of a direct and an indirect network.

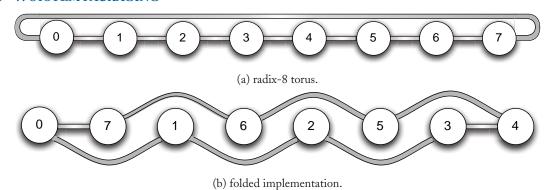

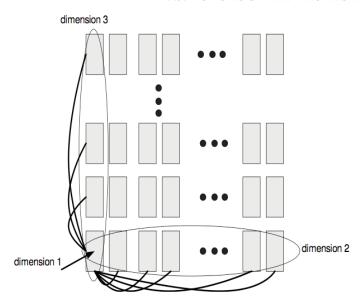

# 3.3 MESH, TORUS, AND HYPERCUBES

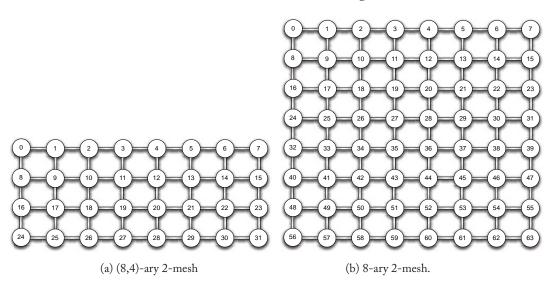

The *mesh*, *torus* and *hypercube* networks all belong to the same family of direct networks often referred to as k-ary n-mesh or k-ary n-cube. The scalability of the network is largely determined by the radix, k, and number of dimensions, n, with  $N = k^n$  total endpoints in the network. In practice, the radix of the network is not necessarily the same for every dimension (Figure 3.2). Therefore, a more general way to express the total number of endpoints is given by Equation 3.1.

$$N = \prod_{i=0}^{n-1} k_i \tag{3.1}$$

Figure 3.1: Mesh (a) and torus (b) networks.

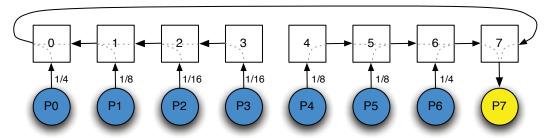

Mesh and torus networks (Figure 3.1) provide a convenient starting point to discuss topology tradeoffs. Starting with the observation that each router in a k-ary n-mesh, as shown in Figure 3.1(a), requires only three ports; one port connects to its neighboring node to the left, another to its right neighbor, and one port (not shown) connects the router to the processor. Nodes that lie along the edge of a mesh, for example nodes 0 and 7 in Figure 3.1(a), require one less port. The same applies to k-ary n-cube (torus) networks. In general, the number of input and output ports, or radix of each router is given by Equation 3.2. The term "radix" is often used to describe both the number of input and output ports on the router, and the size or number of nodes in each dimension of the network.

$$r = 2n + 1 \tag{3.2}$$

The number of dimensions (n) in a mesh or torus network is limited by practical packaging constraints with typical values of n=2 or n=3. Since n is fixed we vary the radix (k) to increase the size of the network. For example, to scale the network in Figure 3.2a from 32 nodes to 64 nodes, we increase the radix of the y dimension from 4 to 8 as shown in Figure 3.2b.

Figure 3.2: Irregular (a) and regular (b) mesh networks.

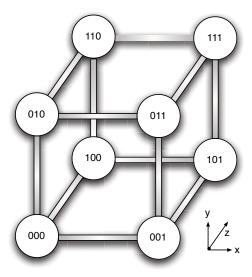

Since a binary hypercube (Figure 3.4) has a fixed radix (k=2), we scale the number of dimensions (n) to increase its size. The number of dimensions in a system of size N is simply  $n = lg_2(N)$ from Equation 3.1.

$$r = n + 1 = \lg_2(N) + 1 \tag{3.3}$$

As a result, hypercube networks require a router with more ports (Equation 3.3) than a mesh or torus. For example, a 512 node 3-D torus (n=3) requires seven router ports, but a hypercube requires  $n = lg_2(512) + 1 = 10$  ports. It is useful to note, an *n*-dimension binary hypercube is isomorphic to

## 22 3. TOPOLOGY BASICS

a  $\frac{n}{2}$ -dimension torus with radix 4 (k=4). Router *pin bandwidth* is limited, thus building a 10-ported router for a hypercube instead of a 7-ported torus router may not be feasible without making each port *narrower*.

## 3.3.1 NODE IDENTIFIERS

The nodes in a k-ary n-cube are identified with an n-digit, radix k number. It is common to refer to a node identifier as an endpoint's "network address." A packet makes a finite number of hops in each of the n dimensions. A packet may traverse an intermediate router,  $c_i$ , en route to its destination. When it reaches the correct ordinate of the destination, that is  $c_i = d_i$ , we have resolved the ith dimension of the destination address.

## 3.3.2 *k*-ARY *n*-CUBE TRADEOFFS

The worst-case distance (measured in hops) that a packet must traverse between any source and any destination is called the *diameter* of the network. The network diameter is an important metric as it bounds the worst-case latency in the network. Since each hop entails an arbitration stage to choose the appropriate output port, reducing the network diameter will, in general, reduce the *variance* in observed packet latency. The network diameter is independent of traffic pattern, and is entirely a function of the topology, as shown in Table 3.1

| Table 3.1: Network diameter and average latency. |          |             |  |  |  |  |  |  |  |

|--------------------------------------------------|----------|-------------|--|--|--|--|--|--|--|

|                                                  | Diameter | Average     |  |  |  |  |  |  |  |

| Network                                          | (hops)   | (hops)      |  |  |  |  |  |  |  |

| mesh                                             | k-1      | (k+1)/3     |  |  |  |  |  |  |  |

| torus                                            | k/2      | k/4         |  |  |  |  |  |  |  |

| hypercube                                        | n        | n/2         |  |  |  |  |  |  |  |

| flattened butterfly                              | n+1      | n+1-(n-1)/k |  |  |  |  |  |  |  |

| from/to          | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |   | from/to | 0     | 1      | 2   | 3 | 4 | 5 | 6 | 7 | 8 |

|------------------|---|---|---|---|---|---|---|---|---|---|---------|-------|--------|-----|---|---|---|---|---|---|

| 0                | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |   | 0       | 0     | 1      | 2   | 3 | 4 | 4 | 3 | 2 | 1 |

| 1                | 1 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |   | 1       | 1     | 0      | 1   | 2 | 3 | 4 | 4 | 3 | 2 |

| 2                | 2 | 1 | 0 | 1 | 2 | 3 | 4 | 5 | 6 |   | 2       | 2     | 1      | 0   | 1 | 2 | 3 | 4 | 4 | 3 |

| 3                | 3 | 2 | 1 | 0 | 1 | 2 | 3 | 4 | 5 |   | 3       | 3     | 2      | 1   | 0 | 1 | 2 | 3 | 4 | 4 |

| 4                | 4 | 3 | 2 | 1 | 0 | 1 | 2 | 3 | 4 |   | 4       | 4     | 3      | 2   | 1 | 0 | 1 | 2 | 3 | 4 |

| 5                | 5 | 4 | 3 | 2 | 1 | 0 | 1 | 2 | 3 | Г | 5       | 4     | 4      | 3   | 2 | 1 | 0 | 1 | 2 | 3 |

| 6                | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 1 | 2 |   | 6       | 3     | 4      | 4   | 3 | 2 | 1 | 0 | 1 | 2 |

| 7                | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 1 |   | 7       | 2     | 3      | 4   | 4 | 3 | 2 | 1 | 0 | 1 |

| 8                | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   | 8       | 1     | 2      | 3   | 4 | 4 | 3 | 2 | 1 | 0 |

| (a) radix-9 mesh |   |   |   |   |   |   |   |   |   |   | (b)     | radiz | c-9 to | rus |   |   |   |   |   |   |

Figure 3.3: Hops between every source, destination pair in a mesh (a) and torus (b).

In a mesh (Figure 3.3), the destination node is, at most, k-1 hops away. To compute the average, we compute the distance from all sources to all destinations, thus a packet from node 1 to

node 2 is one hop, node 1 to node 3 is two hops, and so on. Summing the number of hops from each source to each destination and dividing by the total number of packets sent k(k-1) to arrive at the average hops taken. A packet traversing a torus network will use the wraparound links to reduce the average hop count and network diameter. The worst-case distance in a torus with radix k is k/2, but the average distance is only half of that, k/4. In practice, when the radix k of a torus is odd, and there are two equidistant paths regardless of the direction (i.e., whether the wraparound link is used) then a routing convention is used to break ties so that half the traffic goes in each direction across the two paths.

A binary hypercube (Figure 3.4) has a fixed radix (k=2) and varies the number of dimensions (n) to scale the network size. Each node in the network can be viewed as a binary number, as shown in Figure 3.4. Nodes that differ in only one digit are connected together. More specifically, if two nodes differ in the ith digit, then they are connected in the ith dimension. Minimal routing in a hypercube will require, at most, n hops if the source and destination differ in every dimension, for example, traversing from 000 to 111 in Figure 3.4. On average, however, a packet will take n/2 hops.

**Figure 3.4:** A binary hypercube with three dimensions.

## **SUMMARY**

This chapter provided an overview of direct and indirect networks, focusing on topologies built from low-radix routers with a relatively small number of wide ports. We describe key performance metrics of diameter and average hops and discuss tradeoffs. Technology trends motivated the use of low-radix topologies in the 80s and the early 90s.

## 24 3. TOPOLOGY BASICS

In practice, there are other issues that emerge as the system architecture is considered as a whole; such as, QoS requirements, flow control requirements, and tolerance for latency variance. However, these are secondary to the guiding technology (signaling speed) and packaging and cooling constraints. In the next chapter, we describe how evolving technology motivates the use of *high-radix* routers and how different high-radix topologies can efficiently exploit these *many-ported* switches.

# **High-Radix Topologies**

Dally [18] and Agarwal [5] showed that under fixed packaging constraints, lower radix networks offered lower packet latency. As a result, many studies have focused on low-radix topologies such as the *k*-ary *n*-cube topology discussed in Chapter 3. The fundamental result of these authors still holds – technology and packaging constraints should drive topology design. However, what has changed in recent years are the topologies that these constraints lead us toward. In this section, we describe the high-radix topologies that can better exploit today's technology.

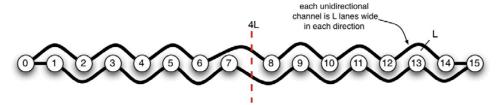

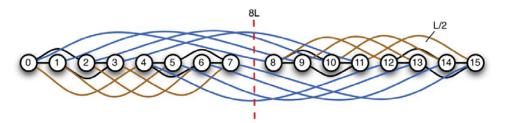

(a) radix-16 one-dimensional torus with each unidirectional link L lanes wide.

(b) radix-4 two-dimensional torus with each unidirectional link L/2 lanes wide.

Figure 4.1: Each router node has the same amount of pin bandwidth but differ in the number of ports.

## 4.1 TOWARDS HIGH-RADIX TOPOLOGIES

Technology trends and packaging constraints can and do have a major impact on the chosen topology. For example, consider the diagram of two 16-node networks in Figure 4.1. The radix-16 one-dimensional torus in Figure 4.1a has *two* ports on each router node; each port consists of an input

and output and are L lanes wide. The amount of pin bandwidth off each router node is  $4 \times L$ . If we partitioned the router bandwidth slightly differently, we can make better use of the bandwidth as shown in Figure 4.1b. We transformed the one-dimensional torus of Figure 4.1a into a radix-4 two-dimensional torus in Figure 4.1b, where we have twice as many ports on each router, but each port is only half as wide — so the pin bandwidth on the router is held constant. There are several direct benefits of the high-radix topology in Figure 4.1b compared to its low-radix topology in Figure 4.1a:

- (a) by increasing the number of *ports* on each router, but making each port *narrower*, we doubled the amount of *bisection bandwidth*, and

- (b) we decreased the average number of hops by half.

The topology in Figure 4.1b requires longer cables which can adversely impact the signaling rate since the maximum bandwidth of an electrical cable drops with increasing cable length since signal attenuation due to skin effect and dielectric absorption increases linearly with distance.

## 4.2 TECHNOLOGY DRIVERS

The trend toward high-radix networks is being driven by several technologies:

- high-speed signaling, allowing each channel to be *narrower* while still providing the same bandwidth,

- affordable optical signaling through CMOS photonics and *active* optical cables that decouple data rate from cable reach, and

- new router microarchitectures that scale to high port counts and exploit the abundant wire and transistor density of modern CMOS devices.

The first two items are described further in this section while the router microarchitecture details will be discussed in Chapter 6.

## 4.2.1 PIN BANDWIDTH

As described earlier in Chapter 2, the amount of total pin bandwidth has increased at a rate of  $100 \times$  over each decade for the past 20-25 years. To understand how this increased pin bandwidth affects the optimal network radix, consider the latency (T) of a packet traveling through a network. Under low loads, this latency is the sum of header latency and serialization latency. The header latency  $(T_h)$  is the time for the beginning of a packet to traverse the network and is equal to the number of hops (H) a packet takes times a per hop router delay  $(t_r)$ . Since packets are generally wider than the network channels, the body of the packet must be squeezed across the channel, incurring an additional serialization delay  $(T_s)$ . Thus, total delay can be written as

$$T = T_h + T_s = Ht_r + L/b \tag{4.1}$$

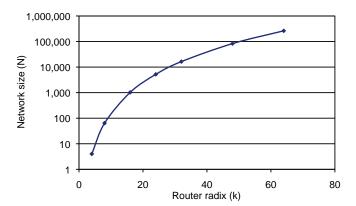

where L is the length of a packet, and b is the bandwidth of the channels. For an N node network with radix k routers (k input channels and k output channels per router), the number of hops must be at least  $2log_kN$ . Also, if the total bandwidth of a router is B, that bandwidth is divided among the 2k input and output channels and b = B/2k. Substituting this into the expression for latency from Equation (4.1)

$$T = 2t_r \log_k N + 2kL/B \tag{4.2}$$

Then, setting dT/dk equal to zero and isolating k gives the optimal radix in terms of the network parameters,

$$k\log^2 k = \frac{Bt_r \log N}{L} \tag{4.3}$$

In this differentiation, we assume B and  $t_r$  are independent of the radix k. Since we are evaluating the optimal radix for a *given* bandwidth, we can assume B is independent of k. The  $t_r$  parameter is a function of k but has only a small impact on the total latency and has no impact on the optimal radix. Router delay  $t_r$  can be expressed as the number of pipeline stages (P) times the cycle time  $(t_{cy})$ . As radix increases, the router microarchitecture can be designed where  $t_{cy}$  remains constant and P increases logarithmically. The number of pipeline stages P can be further broken down into a component that is independent of the radix X and a component which is dependent on the radix  $Y \log_2 k$ . Thus, router delay  $(t_r)$  can be rewritten as

$$t_r = t_{cy}P = t_{cy}(X + Y\log_2 k)$$

(4.4)

If this relationship is substituted back into Equation (4.2) and differentiated, the dependency on radix k coming from the router delay disappears and does not change the optimal radix. Intuitively, although a single router delay increases with a  $\log(k)$  dependence, the effect is offset in the network by the fact that the hop count decreases as  $1/\log(k)$  and as a result, the router delay does not significantly affect the optimal radix.

In Equation (4.2), we also ignore time of flight for packets to traverse the wires that make up the network channels. The time of flight does not depend on the radix(k) and thus has minimal impact on the optimal radix. Time of flight is D/v where D is the total physical distance traveled by a packet, and v is the propagation velocity. As radix increases, the distance between two router nodes increases. However, the *total* distance traveled by a packet will be approximately equal since the lower-radix network requires more hops. <sup>3</sup>

From Equation (4.3), we refer to the quantity  $A = \frac{Bt_r \log N}{L}$  as the aspect ratio of the router [42]. This aspect ratio impacts the router radix that minimizes network latency. A high aspect ratio implies a "tall, skinny" router (many, narrow channels) minimizes latency, while a low ratio implies a "short, fat" router (few, wide channels).

<sup>&</sup>lt;sup>1</sup>Uniform traffic is assumed and  $2log_k N$  hops are required for a non-blocking network.

<sup>&</sup>lt;sup>2</sup>For example, routing pipeline stage is often independent of the radix while the switch allocation is dependent on the radix.

<sup>&</sup>lt;sup>3</sup>The time of flight is also dependent on the packaging of the system but we ignore packaging in this analysis.

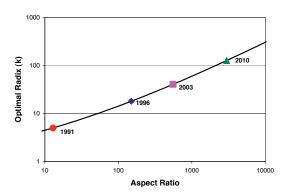

Figure 4.2: Relationship between the optimal radix for minimum latency and router aspect ratio. The labeled points show the approximate aspect ratio for a given year's technology with a packet size of L=128 bits

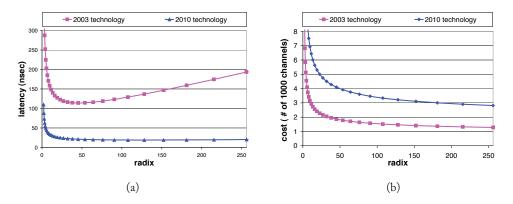

Figure 4.3: Latency (a) and cost (b) of the network as the radix is increased for two different technologies.

A plot of the minimum latency radix versus aspect ratio is shown in Figure 4.2 annotated with aspect ratios from several years. These particular numbers are representative of large supercomputers with single-word network accesses<sup>4</sup>, but the general trend of the radix increasing significantly over time remains. Figure 4.3(a) shows how latency varies with radix for 2003 and 2010 aspect ratios. As radix is increased, latency first decreases as hop count, and hence  $T_h$ , is reduced. However, beyond a certain radix, serialization latency begins to dominate the overall latency and latency increases. As bandwidth, and hence aspect ratio, is increased, the radix that gives minimum latency also increases. For 2004 technology (aspect ratio = 652), the optimum radix is 45 while for 2010 technology (aspect ratio = 3013) the optimum radix is 128.

<sup>&</sup>lt;sup>4</sup>The 1996 data is from the Cray T3E [55] (*B*=48Gb/s, *t<sub>r</sub>*=40ns, *N*=2048), the 2003 data is combined from the Alpha 21364 [49] and Velio VC2002 [20] (1Tb/s, 10ns, 4096), and the 2010 data was estimated as (20Tb/s, 2ns, 8192).

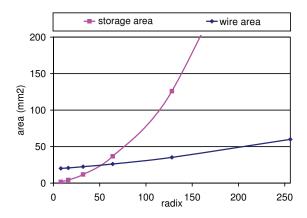

Increasing the radix of networks monotonically reduces the overall cost of a network. Network cost is largely due to router pins and connectors and hence is roughly proportional to total router bandwidth: the number of channels times their bandwidth. For a fixed network bisection bandwidth, this cost is proportional to hop count. Since increasing radix reduces hop count, higher radix networks have lower cost as shown in Figure 4.3(b). Power dissipated by a network also decreases with increasing radix. The network power is roughly proportional to the number of router nodes in the network. As radix increases, hop count decreases, and the number of router nodes decreases. The power of an individual router node is largely independent of radix as long as total router bandwidth is held constant. Router power is largely due to SerDes (serializer/deserializer) I/O circuits and internal switch datapaths. The arbitration logic, which becomes more complex as radix increases, represents a negligible fraction of total power [67].

## 4.2.2 ECONOMICAL OPTICAL SIGNALING

Migrating from low-radix topology to high-radix topology increases the length of the channels as described earlier in Section 4.1. For low-radix routers, the routers are often only connected to neighboring routers – e.g., with a radix-6 router in a 3-D torus network, each router is connect to two neighbors in the x, y, and z dimensions. The long wraparound link of a torus topology can be removed by creating a "folded" torus, as shown in Figure 4.1(a). As a result, the cable lengths are reasonably short and only need to cross one or two cabinets at most and thus often under a few meters in length. The benefit of short cables, under say five meters, is that they can be driven using low-cost *passive* electrical signaling. With a high-radix router, such as a radix-64 router, each router is now connected to a larger number of routers which can be either centrally located or physically distributed, yet far away. Although high-radix reduces the network diameter, it increases the length of the cables required in the system as demonstrated in Figure 4.1(b).

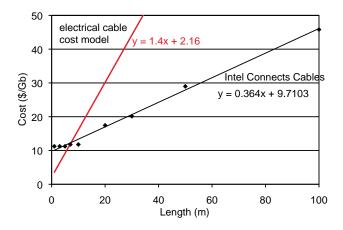

Historically, the high cost of optical signaling limited its use to very long distances or applications that demanded performance regardless of cost. Recent advances in silicon photonics and their application to active optical cables such as Intel Connects Cables [23] and Luxtera Blazar [46, 47] have enabled economical optical interconnect. These active optical cables have electrical connections at either end and EO and OE <sup>5</sup> modules integrated into the cable itself.

Figure 4.4 compares the cost of electrical and optical signaling bandwidth as a function of distance. The cost of Intel Connects Cables[23] is compared with the electrical cable cost model presented in [41]. <sup>6</sup> Optical cables have a higher fixed cost (y-intercept) but a lower cost per unit distance (slope) than electrical cables. Based on the data presented here, the crossover point is at 10m. For distances shorter than 10m, electrical signaling is less expensive. Beyond 10m, optical signaling is more economical. By reducing the number of global cables it minimizes the effect of the higher fixed overhead of optical signaling, and by making the global cables longer, it maximizes

<sup>&</sup>lt;sup>5</sup>EO : Electrical to Optical, OE : Optical to Electrical

<sup>&</sup>lt;sup>6</sup>The optical cost was based on prices available at http://shop.intel.com at the time this analysis was done in 2008 [38]. If purchased in bulk, the prices will likely be lower. The use of multi-mode fiber instead of single-mode fiber may also result in lower cost. Subsequently, the Connects Cables were acquired from Intel by EMCORE Corporation.

Figure 4.4: Cable cost comparison between optical and electrical cables.

the advantage of the lower per-unit cost of optical fibers. The high-radix topologies described in the following section exploits this relationship between cost and distance and thus, exploiting the availability of high-radix routers.

## 4.3 HIGH-RADIX TOPOLOGY

## 4.3.1 HIGH-DIMENSION HYPERCUBE, MESH, TORUS

The direct networks described earlier in Chapter 3 can use high-radix routers to create high-dimension topologies, including hypercube, mesh, and torus. The high-dimension topologies reduce the network diameter, but since the number of routers required for these topologies is proportional to N or the network size, the wiring or the cabling complexity can become prohibitively expensive and also increase the network cost. The indirect networks described earlier in Chapter 3 can better exploit high-radix routers while reduce network cost and wiring complexity. In addition, concentration [20] can be used to where the router is shared among multiple terminal nodes to further reduce the wiring complexity. The topologies that we describe in this chapter leverage concentration to exploit high-radix routers (which enable connecting multiple nodes to a router) and make cabling feasible.

### 4.3.2 BUTTERFLY

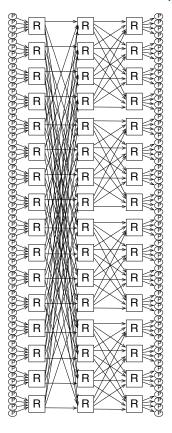

The butterfly network (k-ary n-fly) can take advantage of high-radix routers to reduce latency and network cost [20]. For a network with N nodes and radix-k routers,  $log_k(N) + 1$  stages with N/k routers in each stage are needed. For example, a 64-node butterfly network with radix-4 routers (4-ary 3-fly) is shown in Figure 4.5, with the input nodes shown on the left and the output nodes shown on the right. The butterfly topology minimizes the network diameter and as a result, minimizes network cost. However, there are two noticeable disadvantages of the butterfly network. There is a lack of

Figure 4.5: Conventional Butterfly Topology (4-ary 3-fly) with 64 nodes. P represents the processor or the terminals nodes and R represents the switches or the routers. For simplicity, the network injection ports (terminal ports) are shown on the left while the network ejection ports are shown on the right. However, they represent the same physical terminal nodes.

path diversity in the topology as there is only a single path between any source and any destination. This results in poor throughput for any non-uniform traffic patterns. In addition, a butterfly network cannot exploit traffic locality as all packets must traverse the diameter of the network.

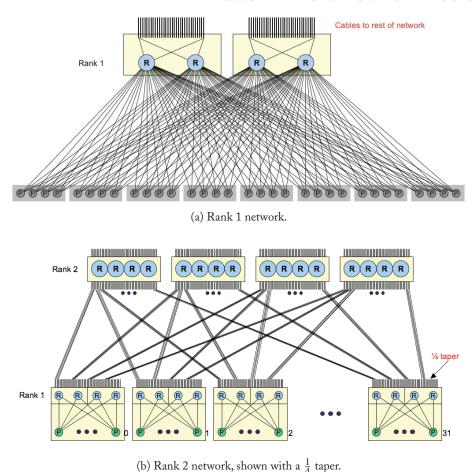

#### **HIGH-RADIX FOLDED-CLOS** 4.3.3

A Clos network [14] is a multi-stage interconnection network consisting of an odd number of stages connecting input ports to output ports (Figure 4.6(a)). The Clos network can be created by combining two butterfly networks back-to-back with the first stage used for load-balancing (input network) and the second stage used to route the traffic (output network). A Clos network provides

**Figure 4.6:** (a) High-Radix Clos topology and (b) corresponding folded-Clos topology. The channels in the folded-Clos represent bidirectional channels. The routers in the right-most column of (b) are radix-4 while the others in (b) are radix-8. If the same radix-8 routers need to be used in the folded-Clos network, two radix-4 routers can be combined into a single radix-8 router.

many paths – one for each middle-stage switch in the Clos – between each pair of nodes. This path diversity enables the Clos to route arbitrary traffic patterns with no loss of throughput.

Like a butterfly  $(k\text{-}ary\ n\text{-}fly)$  network, a folded-Clos is also an *indirect* network. The router nodes are distinct from the endpoints. The first tier of the network connects k/2 hosts (endpoints) to the switch, and k/2 *uplinks* to other switches in the next tier. If the injection bandwidth is balanced with the uplink bandwidth, we refer to the network as *fully provisioned*; however, if there is more injection bandwidth than uplink bandwidth, then it is *oversubscribed*. Oversubscription is common in datacenter applications since it reduces cost and improves utilization. The input and output stages

**Figure 4.7:** Deriving a Flattened Butterfly from a conventional butterfly shown in Figure 4.5.

of a Clos network can be combined or *folded* on top of one another creating a folded Clos or fattree [44] network which can exploit traffic locality with the input/output ports co-located, as shown in Figure 4.6(b).

A Clos or folded Clos network, however, has a cost that is nearly double that of a butterfly with equal capacity and has greater latency than a butterfly. The increased cost and latency both stem from the need to route packets first to an arbitrary middle stage switch and then to their ultimate destination. This doubles the number of long cables in the network, which approximately doubles cost, and doubles the number of inter-router channels traversed, which drives up latency.

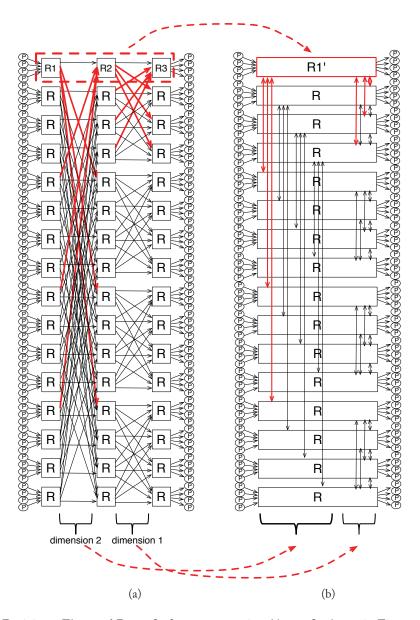

## 4.3.4 FLATTENED BUTTERFLY

To overcome the limitations of the folded-Clos topology, the flattened butterfly [41] removes intermediate stages and creates a *direct* network. As a result, the flattened butterfly is a topology that exploits high-radix routers to realize lower cost than a Clos on load-balanced traffic, and provide better performance and path diversity than a conventional butterfly. The flattened butterfly can be derived by starting with a conventional butterfly (*k*-ary *n*-fly) and combining or *flattening* the routers in each *row* of the network into a single router. An example of flattened butterfly construction is shown in Figure 4.7. 4-ary 3-fly network is shown in Figure 4.7(a) with the corresponding flattened butterflies shown in Figure 4.7(b). The routers R1, R2, and R3 from the first row of Figure 4.7(a) are combined into a single router R0′ in the flattened butterfly of Figure 4.7(b). As a row of routers is combined, channels entirely local to the row, e.g., channel (R0,R1) in Figure 4.7(a), are eliminated. All other channels of the original butterfly remain in the flattened butterfly. Because channels in a flattened butterfly are symmetrical, each line in Figures 4.7(b) represents a bidirectional channel (i.e., two unidirectional channels), while each line in Figures 4.7(a) represents a unidirectional channel.

A k-ary n-flat, the flattened butterfly derived from a k-ary n-fly, is composed of  $\frac{N}{k}$  radix k' = n(k-1) + 1 routers where N is the size of the network. The routers are connected by channels in n' = n - 1 dimensions, corresponding to the n - 1 columns of inter-rank wiring in the butterfly. In each dimension d, from 1 to n', router i is connected to each router j given by

$$j = i + \left[ m - \left( \left\lfloor \frac{i}{k^{d-1}} \right\rfloor \mod k \right) \right] k^{d-1}$$

(4.5)

for m from 0 to k-1, where the connection from i to itself is omitted. For example, in Figure 4.7(d), R4′ is connected to R5′ in dimension 1, R6′ in dimension 2, and R0′ in dimension 3. With this construction, it is easy to see that the flattened butterfly is equivalent to the *generalized hypercube* topology [10], but with k-way concentration. With this concentration, the topology is better able to exploit the properties of high-radix routers.

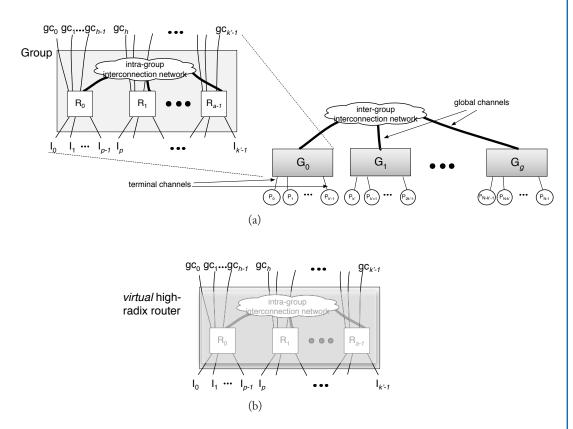

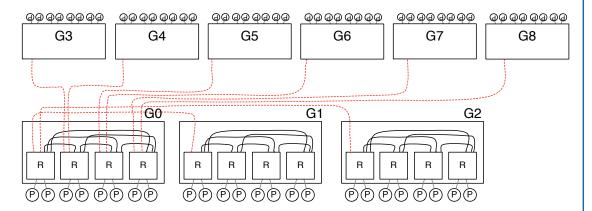

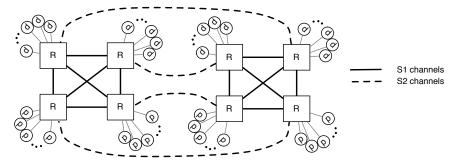

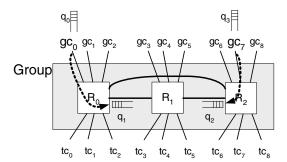

## 4.3.5 DRAGONFLY

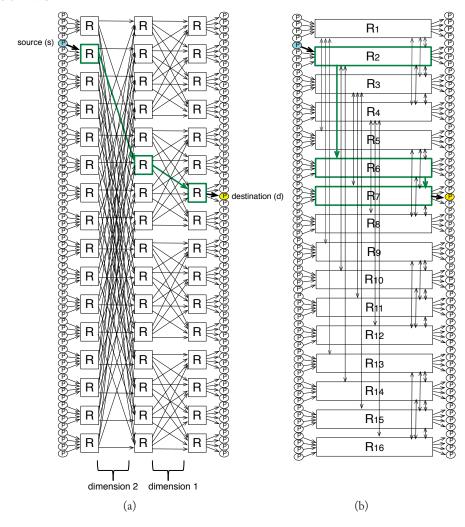

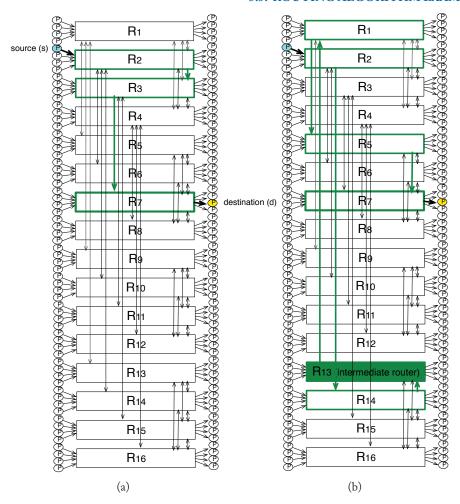

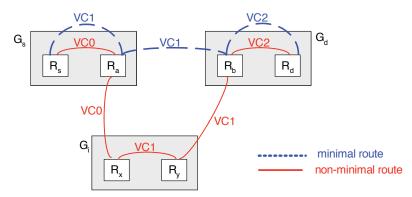

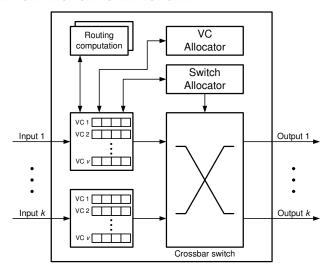

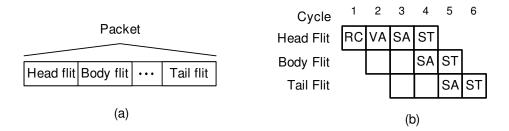

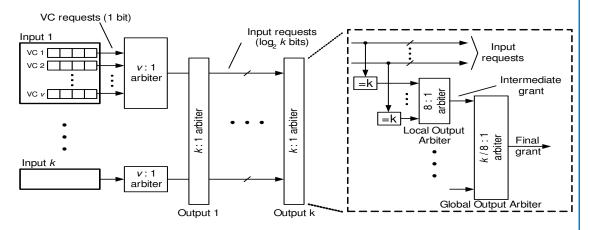

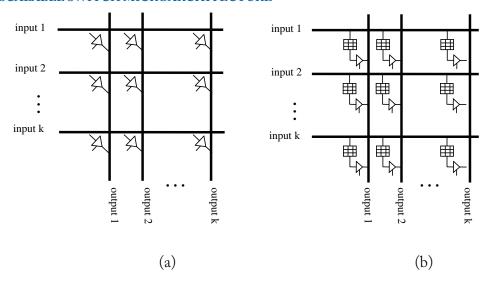

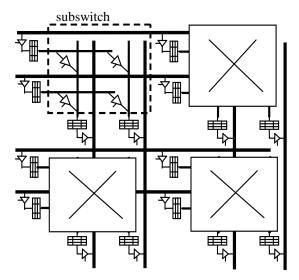

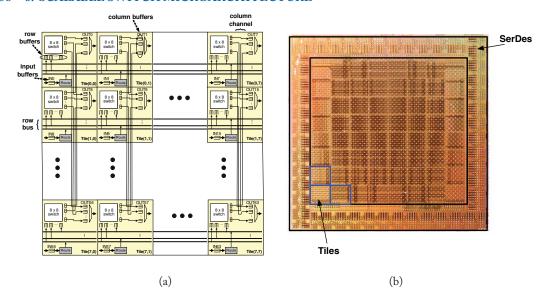

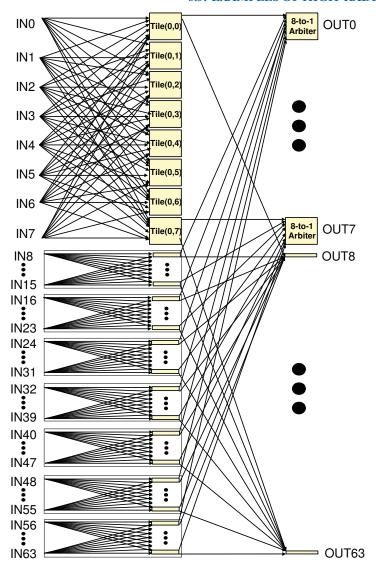

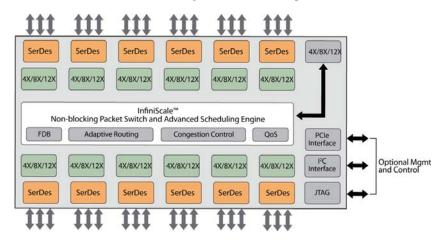

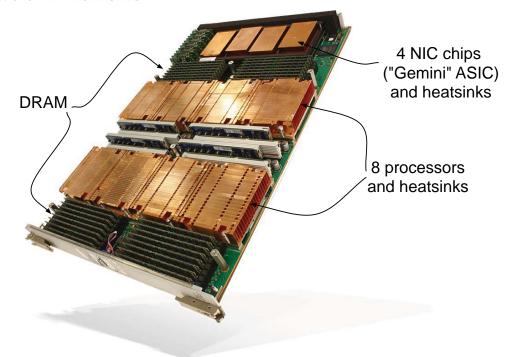

Although the flattened butterfly can cost-efficiently exploit high-radix routers, it is ultimately limited by the physical constraints of a router radix and cost of scaling to large node count. For example, if